International Journal of Extreme Manufacturing

# Low voltage and robust InSe memristor using van der Waals electrodes integration

Qianyuan Li, Quanyang Tao, Yang Chen, Lingan Kong, Zhiwen Shu, Huigao Duan, Lei Liao and Yuan Liu

## **Highlights:**

- A van der Waals (vdW) memristor by physically sandwiching pre-fabricated metal electrodes on both sides of the two-dimensional channel material is demonstrated for the first time.

- The memristor arrays shows a high integration density of 10<sup>10</sup> cm<sup>-2</sup>, a high stability and the lowest set/reset voltage of 0.12V/0.04V, which is a record low value for all 2D-based memristors.

- The improved memristor behavior is confirmed the result of optimized BE/channel and TE/channel interfaces.

- A general electrode integration approach is provided for other 2D memristors which have previously been limited by non-ideal contact integration, high operation voltage and poor device stability.

## View online:https://iopscience.iop.org/article/10.1088/2631-7990/ac2296

## Article Download: https://iopscience.iop.org/article/10.1088/2631-7990/ac2296/pdf

**Citation:** Li Q Y, Tao Q Y, Chen Y, Kong L G, Shu Z W et al. Low voltage and robust InSe memristor using van der Waals electrodes integration *Int. J. Extrem. Manuf.* **3**, 045103 (2021).

# **Related articles:**

Self-limiting laser crystallization and direct writing of 2D materials

Zabihollah Ahmadi, Baha Yakupoglu, Nurul Azam, Salah Elafandi and Masoud Mahjouri-Samani

**Citation:** Ahmadi Z, Yakupoglu B, Azam N, Elafandi S, Mahjouri-Samani M. Self-limiting laser crystallization and direct writing of 2D materials. *Int. J. Extrem. Manuf.* **1**, 015001 (2019).

Atomic level deposition to extend Moore's law and beyond

Rong Chen, Yi-Cheng Li, Jia-Ming Cai, Kun Cao and Han-Bo-Ram Lee

**Citation:** Chen R, Li Y C, Cai J M, Cao Kun, Lee H B R. Atomic level deposition to extend Moore's law and beyond. *Int. J. Extrem. Manuf.* **2**, 022002 (2020).

Sub-10 nm fabrication: methods and applications

Yiqin Chen, Zhiwen Shu, Shi Zhang, Pei Zeng, Huikang Liang, Mengjie Zheng and Huigao Duan

**Citation:** Chen Y Q, Shu Z W, Zhang S, Zeng P, Liang H K et al. Sub-10 nm fabrication: methods and applications. *Int. J. Extrem. Manuf.* **3**, 032002(2021).

OPEN ACCESS

Int. J. Extrem. Manuf. 3 (2021) 045103 (8pp)

https://doi.org/10.1088/2631-7990/ac2296

# Low voltage and robust InSe memristor using van der Waals electrodes integration

# Qianyuan Li<sup>1</sup>, Quanyang Tao<sup>1</sup>, Yang Chen<sup>1</sup>, Lingan Kong<sup>1</sup>, Zhiwen Shu<sup>2</sup>, Huigao Duan<sup>2</sup>, Lei Liao<sup>1</sup> and Yuan Liu<sup>1,\*</sup>

<sup>1</sup> Key Laboratory for Micro-Nano Optoelectronic Devices of Ministry of Education, School of Physics and Electronics, Hunan University, Changsha 410082, People's Republic of China

<sup>2</sup> State Key Laboratory of Advanced Design and Manufacturing for Vehicle Body, School of Mechanical and Vehicle Engineering, Hunan University, Changsha 410082, People's Republic of China

E-mail: yuanliuhnu@hnu.edu.cn

Received 13 July 2021, revised 8 August 2021 Accepted for publication 31 August 2021 Published 5 October 2021

#### Abstract

Memristors have attracted tremendous interest in the fields of high-density memory and neuromorphic computing. However, despite the tremendous efforts that have been devoted over recent years, high operating voltage, poor stability, and large device variability remain key limitations for its practical application and can be partially attributed to the un-optimized interfaces between electrodes and the channel material. We demonstrate, for the first time, a van der Waals (vdW) memristor by physically sandwiching pre-fabricated metal electrodes on both sides of the two-dimensional channel material. The atomically flat bottom electrode ensures intimate contact between the channel and electrode (hence low operation voltage), and the vdW integration of the top electrode avoids the damage induced by aggressive fabrication processes (e.g. sputtering, lithography) directly applied to the channel material, improving device stability. Together, we demonstrate memristor arrays with a high integration density of  $10^{10}$  cm<sup>-2</sup>, high stability, and the lowest set/reset voltage of 0.12 V/0.04 V, which is a record low value for all 2D-based memristors, as far as we know. Furthermore, detailed characterizations are conducted to confirm that the improved memristor behavior is the result of optimized metal/channel interfaces. Our study not only demonstrates robust and low voltage memristor, but also provides a general electrode integration approach for other memristors, such as oxide based memristors, that have previously been limited by non-ideal contact integration, high operation voltage and poor device stability.

Keywords: 2D-material, robust memristor, ultra-low threshold, atomically flat interfaces

#### 1. Introduction

Memristors have attracted considerable attention for neuromorphic computing [1-6] and high-density memory [7-12].

Original content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI. However, despite the tremendous efforts devoted over recent years, the poor stability [6, 13] and large device variability [14, 15] remain key limitations for its practical application. Although the cell-to-cell variability can be addressed with more controllable fabrication conditions (e.g. industrycompatible processing line), the large cycle-to-cycle variability is intrinsically inherited from the device structure and can be partially attributed to the non-ideal interfaces between the metal electrodes and the active channel. From the structural point of view, a typical vertical memristor has a three-layer metal/channel/metal sandwich structure with two interfaces:

<sup>\*</sup> Author to whom any correspondence should be addressed.

the bottom electrode (BE)/channel interface and the top electrode (TE)/channel interface, both of which are imperative for device operation and could greatly impact memristor reproducibility and stability. For example, noble metals (e.g. Au, Pt) favor the formation of isolated islands or percolated networks during initial substrate deposition, leading to a BE surface roughness  $\sim$  1–3 nm, which can further increase to tens or hundreds of nanometers after the BE annealing process [16]. Such a rough BE/channel interface results in non-uniform channel materials with localized strain, random band-structures, and electrical properties, leading to a variable electrical field distribution and large cycle-to-cycle variability. On the other hand, conventional TE metals are fabricated through direct deposition techniques based on the vaporization of precursor materials (e.g. thermal/e-beam evaporation or sputtering) and usually involve repeated bombardment by high-energy hot metal atoms or atomic clusters, resulting in considerable interface damage, metal diffusion into the channel [17], and non-repeatable device behavior. This TE contact damage is particularly fatal for ultra-thin vertical memristors where the TE contact region is essentially the entire channel, leading to greatly enhanced leakage current, device instability, and eventually device failure.

Various efforts have been devoted to improving memristor stability, cycling endurance, and parameter reproducibility. Early attempts used a buffer layer to construct a bilayer channel structure with improved stability and performance [18–20]. For example, an intermediate  $HfO_X$  layer between the TE metal and HfO2 active channel was demonstrated to significantly influence the switching behavior and was an essential part of reliable device operation, where the intermediate suboxide mediated oxygen ion movement, serving as a buffer for redox reactions. However, the insertion of an oxide buffer could increase the device's overall resistance with high set/reset voltage over 3 V/1.6 V [19]. Alternatively, robust memristor operation was demonstrated by using a twodimensional (2D) semiconductor MoS<sub>2</sub> as the active channel and 2D graphene as both the TE and BE [21]. The danglingbond free 2D surface (MoS<sub>2</sub> and graphene) offers atomically sharp and clean interfaces within the TE/channel and BE/channel interfaces [22], overcoming previous limitations from BE roughness and TE deposition induced damage, hence demonstrating improved device stability with working temperatures over 340 °C. Nevertheless, the relatively low conductivity of graphene electrodes leads to excess series resistance, and the inert graphene electrodes prohibit the low voltage electrochemical metallization (ECM) mechanism, limiting the set/reset voltage to 1.2 V/1.1 V. The resistance limiting effect may become more pronounced with increasing integration density by reducing the graphene electrode width (e.g. scaled below 100 nm into graphene nanoribbons).

Here, we demonstrate a new approach for low voltage and robust memristor operation by using InSe as the active channel and damage-free van der Waals (vdW) metals as both the BE (Au) and TE (Ag). By mechanically laminating and sandwiching prefabricated metal electrodes with atomically flat surfaces on both sides of an ultra-thin InSe, the intrinsic channel material can be well retained without conventional metal deposition induced damage. More importantly, the interfaces of both the BE/channel and TE/channel are atomically clean and sharp, overcoming the previous limitations of poor interface quality (e.g. point-contact, inhomogeneous channel), hence, leading to improved device stability and reduced operation voltage. Together, we demonstrate memristor arrays with a high integration density of  $10^{10}$  cm<sup>-2</sup>

and operation duration over 400 cycles, which is a four-fold increase compared to the control sample using conventional deposited BE and TE. Notably, with desired vdW metal/channel interfaces, the channel thickness can be scaled to 1.6 nm with an ultra-low set/reset voltage of 0.12 V/0.04 V, which is a record low value for 2D based memristors, to the best of our knowledge. Furthermore, detailed characterizations are conducted to investigate the impact of BE roughness and TE deposition induced damages, confirming that the improved memristor behavior is the result of optimized metal/channel interfaces in both BE and TE. Our study not only demonstrates a reliable and low voltage memristor, but also provides a general electrode integration approach for other memristors or other ultra-thin vertical devices that are previously limited by non-ideal contact integration and poor device stability.

#### 2. Results and discussion

#### 2.1. Fabrication flow of vdW memristors

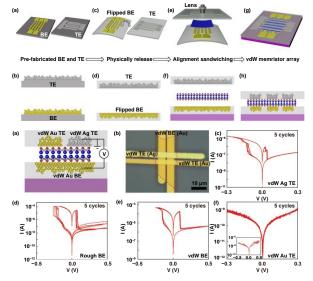

Figure 1 schematically illustrates the process flow for fabricating our memristor with both vdW TE and BE contact. First, Au and Ag (both 50 nm thick) metal electrode arrays are prefabricated on two separate Si substrates, as shown in figures 1(a) and (b). They can be mechanically released from the substrate using a previously developed method [23] and demonstrate an atomically flat surface, replicating the flat surface of the silicon substrate (details in the Methods section). Next, the released Au electrode arrays (used as BE) are flipped and placed on a SiO<sub>2</sub> substrate, where the flat surface is facing up, as schematically shown in figures 1(c) and (d). In this way, we achieved flat BE arrays to overcome the previous limitation of surface roughness. Then, a few layers of InSe flake are used as the channel material and integrated on top of the BE arrays using a standard dry alignment transfer process, forming an intimate contact with the BE and a uniform Au/InSe interface (figures 1(e) and (f)). Finally, the previously released Ag electrode arrays are mechanically laminated on top of the InSe channel as the TE contact, forming a crossbar structure with the BE, as shown in figures 1(g) and (h). Notably, the vdW integration process of the TE also leads to an atomically clean and electrically sharp TE/InSe interface, which is essential to maintain the intrinsic properties of the ultra-thin channel and to improve the device's overall uniformity and reproducibility. This is in significant contrast to the conventional TE direct deposition process, which involves repeated bombardment of the channel by high-energy hot atoms or atomic clusters,

**Figure 1.** (a), (b) Perspective (a) and cross-sectional (b) schematics of prefabricated BE and TE arrays on two separated silicon substrates; (c), (d) perspective (c) and cross-sectional (d) schematics of the released BE and TE arrays. The released BE arrays are flipped with the atomically flat surface; (e), (f) perspective (e) and cross-sectional (f) schematics of the alignment sandwiching process of the BE, InSe, and TE under an optical microscope; (g), (h) perspective (g) and cross-sectional (h) schematics of the vdW memristor arrays with atomically flat interfaces.

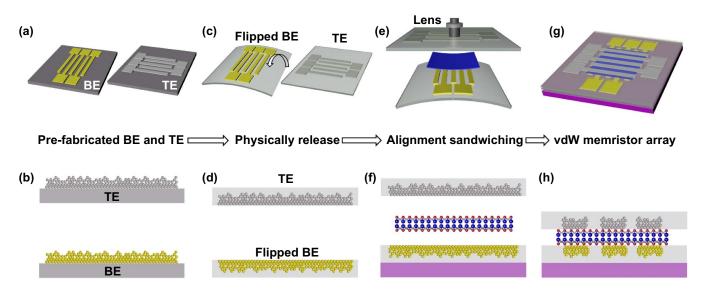

**Figure 2.** Optical image (a) and scanning electron microscope image (b) of memristor arrays with 50 nm electrode width and 100 nm pitch size. Thickness of electrodes is 20 nm.

leading to considerable interface damage, metal diffusion into the channel [17, 24], and non-repeatable device behavior, particularly in ultra-thin channels.

Using the above fabrication process, we achieved memristor crossbar arrays with the intrinsic 2D channel sandwiched between two flat metals based on physical lamination processes. We note that the demonstrated vdW electrode lamination processes (of both TE and BE) are compatible with high density crossbar memristors. Figure 2 shows memristor arrays with 50 nm line width and 100 nm pitch size (the size of the array is dependent on the exfoliated film), corresponding to a high integration density of  $10^{10}$  cm<sup>-2</sup>. Further reducing the pitch size can lead to the contact between two neighbor electrodes (and device short) due to the strain generated during the vdW integration process.

#### 2.2. Electrical performance and the memristive mechanism

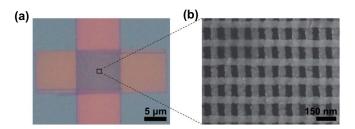

Electrical transport studies of the vdW memristor are carried out at room temperature in a Lakeshore probe-station under vacuum conditions ( $10^{-5}$  torr). For the measurement of all devices, the TE is grounded, and the BE is always biased (figures 3(a) and (b)). As shown in figures 3(c), a vdW memristor with a bilayer InSe channel (1.6 nm thick) exhibits bipolar resistive switching and nonvolatile behavior with the lowest set/reset voltages at 0.12 V/0.04 V, which is the lowest recorded value of all 2D-based memristors. The observed low switching voltages are important for neuromorphic computing and can be largely attributed to several geometric advantages of our vdW structure. First, the vdW integration of TE metals minimizes conventional fabrication induced damage to channel material, enabling a highly scaled channel thickness of 1.6 nm while retaining intrinsic channel properties. The ultra-thin body thickness is crucial to reduce the bias voltage required for Ag filament formation and then the reduced set/reset voltage [25]. On the other hand, the atomically flat BE surface ensures intimate BE/channel contact with low contact resistance in contrast to the conventional rough BE with a much smaller metal-2D contact area (point-like contact in rough BE/channel interface) with higher contact resistance, as shown in figures 3(d) and (e). The low BE contact resistance reduces the undesired voltage drop in the contact region and further decreases the overall set/reset voltage. Furthermore, the vdW metal electrode's (Ag or Au) contact resistance shows lower series resistance compared to previously used graphene electrodes [21], which also helps to reduce undesired voltage drop.

Beyond the vdW interfaces, the use of Ag as the TE metal is another important contributing factor for the low set/reset voltage achieved. Owning to the active nature of Ag atoms, our vdW memristor can be an ECM device, whereas previous memristors based on layered MoS<sub>2</sub> channels are more likely to be valence change memory (VCM) devices [21, 26]. ECM devices generally exhibit lower operation voltage [27] due to the lower energy required for metal filament formation. To

**Figure 3.** (a), (b) Schematic illustration (a) and optical image (b) of two parallel vdW memristors on the same InSe flake. These devices are fabricated using the same batch of processes, where the TE is Ag in one device and Au in another device. The red dashed line represents the bilayer InSe flake; (c) I-V curve of vdW Ag/InSe/Au memristor with clear switching behavior and low operation voltage; (d), (e) memristor performance using rough BE and vdW BE, respectively; (f) I-V curve of parallel vdW Au/InSe/Au device without any resistive switching behavior, suggesting the ECM mechanism of our vdW memristor. The insert is the output curve while bias voltage increases to 0.8 V.

confirm the ECM working mechanism in our devices, another parallel Au TE is vdW integrated on the same InSe/BE heterostructures using the same batch of fabrication (figures 3(a) and (b)). As shown in figure 3(f), the control device (Au/In-Se/Au) does not demonstrate any resistive switching behavior even bias increases to 0.8 V. This is in contrast to the preferred memristive behavior within the parallel Ag/InSe/Au vdW structure, suggesting the Ag electrode is essential for memristor operation, consistent with previous ECM mechanisms based on Ag filament formation [28].

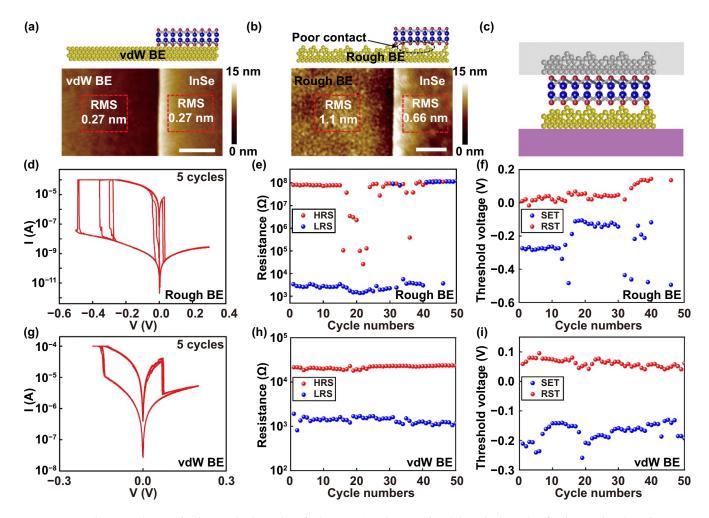

#### 2.3. Comparison of memristors with rough BE and vdW flat BE

To further investigate device stability and demonstrate the importance of the vdW BE/channel interface, we fabricated memristors using both evaporated rough BE and vdW flat BE, while increasing the channel thickness to 2.4 nm and using vdW Ag TE consistently. First, atomic force microscopy is conducted to characterize the surface morphology of both BEs after integrating the InSe channel. As shown in figure 4(a), the vdW Au BE demonstrates an atomically flat surface with a root mean square (RMS) roughness of 0.27 nm. Importantly, the RMS remains unchanged after integrating the InSe channel, suggesting intimate contact between the BE/channel interface, as schematically illustrated in figure 4(a). Conversely, the as-deposited Au BE shows rough surface with a large RMS of 1.1 nm, which is consistent with previous reports [29]. In particular, the surface RMS reduces to 0.6 nm after integrating

the InSe channel on top of this rough BE (figure 4(b)), indicating the InSe channel does not follow the surface morphology of the underlying BE and poor contact (i.e. insufficient and localized contact area) within the conventional BE/channel interface, as schematically illustrated in figure 4(c). Such a rough BE/channel interface results in non-uniform channels with localized strain and random band structures and channel conductivity, leading to variable electrical field distribution and large cycle-to-cycle variability (figure 4(d)). Based on the measurement of the first 50 cycles, the device with rough BE demonstrates highly variable switching behavior. As shown in figures 4(e) and (f), resistances of the high resistance state (HRS) and the low resistance state (LRS) are randomly distributed in the range of  $10^3 \Omega$  to  $10^8 \Omega$  with 5 orders of magnitude of variation. Similarly, the set/reset voltage shows large variation between 0.1 V and 0.5 V.

In contrast, devices with vdW flat BE demonstrates significantly less cycle-to-cycle variability. As shown in figure 4(g), the multicycle measurement exhibits nearly identical characteristics. The extracted HRS and LRS resistances remains relatively stable and demonstrate similar values within first 50 cycles. Furthermore, the set/reset voltage is distributed in much narrower ranges of 0.15 V to 0.25 V and 0.04 V to 0.09 V (figures 4(h) and (i)), respectively, which are nearly an order of magnitude improvement compared to the device with rough BE. Moreover, after 400 cycles, the device still demonstrates a uniform memristor phenomenon while the rough BE device fails to switch resistance after 100 cycles, as shown in figure 5. The above comparisons clearly illustrate the importance of

**Figure 4.** (a), (b) AFM characterizations and schematics of vdW BE (a) and conventional deposited BE (b) after integrating the InSe channel. In particular, the RMS roughness of deposited BE in red dashed line reduces from 1.1 nm to 0.6 nm by integrating InSe, suggesting poor BE/channel contact. Scale bars are 0.5  $\mu$ m; (c), (d) schematic and *I*–*V* measurement of the control device with rough BE/channel interface; (e), (f) distribution statistics of HSR/LSR resistance (e) and set/reset voltage (f) with 50 cycles, where large device variations are observed; (g)–(i) electrical properties of a vdW memristor (with flat BE surface) with 50 cycles, demonstrating smaller device variations and suggesting the importance of the BE/channel interface.

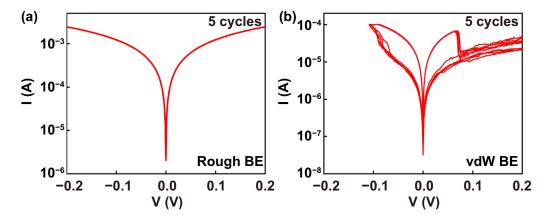

**Figure 5.** (a) I-V curve of memristor with rough BE after 100 cycles measurement, where the linear curve is always observed, suggesting device failure; (b) I-V curve of the memristor with vdW BE after 400 cycles measurement, where the memristor behavior is well-retained.

BE surface roughness for device stability and suggest that the vdW flat BE is essential for stable memristor operation. Furthermore, we note that the integration of an atomically flat BE for other oxide-based memristors [30, 31] or organic based memristors [32] would be an interesting topic for future investigation.

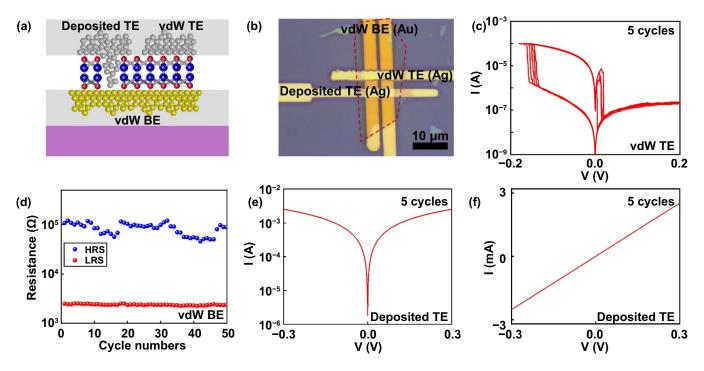

**Figure 6.** (a), (b) Schematic and optical image of the devices on the same InSe flake, where the TE of one device is vdW integrated and another is directly deposited. Red dashed line represents the 3.2 nm thick InSe flake; (c), (d) I-V curve and the distribution statistics of the device with vdW TE, demonstrating desired memristor behavior; (e), (f) Electrical measurement of the parallel device with directly deposited TE, showing the short-circuit and suggesting that conventional TE fabrications induce considerable damage.

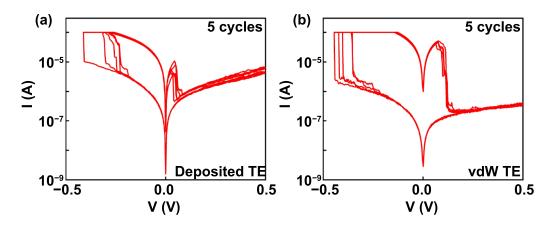

Figure 7. (a), (b) I-V output curves of memristors with deposited TE (a) and vdW TE (b), where clear switching behavior is observed in both devices with 6.4 nm channel thickness.

#### 2.4. Comparison of memristors with high-energy deposited TE and low energy vdW TE

Finally, in order to investigate the impact of TE to memristor reproducibility and stability, we fabricated Ag/InSe/Au devices using conventional deposited Ag TE as well as our vdW integrated Ag TE on the same InSe flake, as shown in figures 6(a) and (b). The detailed device fabrication process is described in the Methods section. An atomically flat BE is consistently used in both devices to provide a fair comparison. As shown in figure 6(c), the device with vdW TE demonstrates robust and low voltage memory behavior within multi-cycle measurements. Figure 6(d) further summarizes the HRS/LRS resistance distribution, which demonstrates uniform device operation consistent with the previous electrical measurement in figure 4. In contrast, the memristor behavior is totally lost in the control device that uses conventional directly deposited TE on the same InSe flake, as shown in figures 6(e) and (f). During multi-cycle measurements, the as-fabricated device always exhibits a linear I-V curve with low resistance (~100  $\Omega$ ), suggesting a short circuit between TE and BE. This could be largely attributed to the conventional aggressive TE fabrication process directly performed on the channel material (e.g. high-energy lithography, wet-chemical development, and high temperature metal deposition), leading to considerable damage and metal diffusion into the channel material as have been characterized through transmission electron microscopy (TEM) in previous literature [17] and schematically illustrated in figure 6(a).

We note that the TE deposition induced damage and device failure become more pronounced when scaling the channel thickness. For all devices with channel thickness below 3.2 nm, the device failure (short circuit) and linear I-V curve are consistently observed when using directly deposited TE, without any memristor behavior, limiting device thickness scaling to low voltage applications. While the channel thickness increases beyond 6.4 nm, devices using deposited TE re-exhibit memristor behavior, as shown in figure 7. However, large cycle-to-cycle variation (over 0.2 V) and smaller HRS/LSR ratio (over 10) are still observed within these devices, further confirming the unoptimized device behavior using directly deposited TE techniques.

### 3. Summary

In conclusion, we demonstrated a vdW memristor by physically sandwiching pre-fabricated electrode arrays on both sides of an InSe channel. The fabricated device shows high integration density, high device stability, and low operation voltage compared to the device fabricated using conventional rough BE or directly deposited TE. Furthermore, detailed characterizations were conducted to confirm that the improved memristor behavior resulted from the optimized BE/channel and TE/channel interfaces. Our study not only demonstrates a robust InSe memristor with the lowest operation voltage, but also provides a general electrode integration approach for 2D memristors. It may also provide exciting implications for oxide-based memristors or other ultra-thin electronic devices that are limited by poor device stability or non-ideal interfaces.

#### 4. Methods

#### 4.1. Fabrication process of vdW electrodes memristors

First, 50 nm thick Au electrode arrays (used as BE) and 30 nm/20 nm thick Ag/Au electrode arrays (used as TE) are thermally deposited onto two separate sacrificial silicon substrates with atomically flat surfaces. Next, 500 nm thick polymethyl methacrylate is spin-coated on the pre-fabricated electrode arrays after hexamethyldisilazane treatment [17], working as a protection layer. Au electrodes are then mechanically released and flipped upside down, so the atomically flat surface faces up, as schematically illustrated in figures 1(c) and (d). Finally, a few layers of InSe flake (mechanically exfoliated for all devices) and Ag/Au electrodes (released from another substrate using the above approach) are successively vdW integrated onto the flat surface, to form the vdW memristor structure.

# 4.2. Fabrication of memristor with parallel vdW TEs using Ag and Au metal

To fabricate the control device with both Ag and Au electrodes in figure 3, asymmetric electrodes pair are pre-fabricated on a sacrificial silicon substrate using two times thermal deposition, where one electrode consists of 50 nm thick Au and the other consists of 30 nm/20 nm thick Ag/Au. The pair of asymmetric electrodes are released and physically laminated on top of a BE/InSe heterostructure, forming two parallel vdW memristors (one Ag/InSe/Au and the other Au/InSe/Au) on the same InSe flake.

#### 4.3. Fabrication of memristor with deposited and vdW TEs

To fabricate the control device with both deposited and vdW TE in figure 6, a few layers of InSe are first exfoliated on a SiO<sub>2</sub> substrate. A 30 nm/20 nm thick Ag/Au electrode is then vdW integrated on the InSe channel using the previously described method. Next, another parallel electrode (also 30 nm/20 nm thick Ag/Au) is directly deposited on the same InSe flake using vacuum thermal evaporation. Finally, the InSe channel with two different electrodes is transferred on top of a BE with an atomically flat surface, as shown in figures 6(a) and (b). Using this approach, we achieved control over memristors on the same InSe channel, with one vdW TE and another directly deposited TE.

#### 4.4. Electrical measurement

Electrical transport studies of all memristors are carried out at room temperature in a Lakeshore PS-100 cryogenic probe station under vacuum conditions ( $10^{-5}$  torr), using Keysight B2900A source measurement unit.

#### Acknowledgments

The authors acknowledge the financial support of the National Natural Science Foundation of China (Nos. 51991340, 51991341, 51802090, and 61874041) and the Hunan Science Fund for Excellent Young Scholars (No. 812019037).

#### Author contributions

Y L conceived the research. Y L and Q L designed the experiments. Q L fabricated the samples and performed the device measurement. Q T, L K, Y C and L L contributed to the discussion of results and manuscript editing. Z S and H D aided in fabricating the high-density electrode arrays. Y L and Q L co-wrote the manuscript. All authors discussed the results and commented on the manuscript.

#### **Conflict of interest**

The authors declare no competing interests.

#### **ORCID** iDs

Huigao Duan b https://orcid.org/0000-0001-9144-2864 Yuan Liu b https://orcid.org/0000-0002-0024-9290

#### References

- [1] Jo S H, Chang T, Ebong I, Bhadviya B B, Mazumder P and Lu W 2010 Nanoscale memristor device as synapse in neuromorphic systems *Nano Lett.* **10** 1297–301

- [2] Hu M, Li H, Chen Y R, Wu Q, Rose G S and Linderman R W 2014 Memristor crossbar-based neuromorphic computing system: a case study *IEEE Trans. Neural Netw. Learn. Syst.* 25 1864–78

- [3] Wang S, Wang W S, Yakopcic C, Shin E, Subramanyam G and Taha T M 2017 Experimental study of LiNbO<sub>3</sub> memristors for use in neuromorphic computing *Microelectron. Eng.* 168 37–40

- [4] Wang Z R *et al* 2017 Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing *Nat. Mater.* 16 101–8

- [5] Zhang X J, Huang A P, Hu Q, Xiao Z S and Chu P K 2018 Neuromorphic computing with memristor crossbar *Phys. Status Solidi* a 215 1700875

- [6] Yan X B et al 2019 Vacancy-induced synaptic behavior in 2D WS<sub>2</sub> nanosheet-based memristor for low-power neuromorphic computing *Small* 15 1901423

- [7] Zidan M A, Fahmy H A H, Hussain M M and Salama K N 2013 Memristor-based memory: the sneak paths problem and solutions *Microelectron. J.* 44 176–83

- [8] Rabbani P, Dehghani R and Shahpari N 2015 A multilevel memristor–CMOS memory cell as a ReRAM *Microelectron. J.* 46 1283–90

- [9] Ali S, Bae J, Lee C H, Shin S and Kobayashi N P 2017 Ultra-low power non-volatile resistive crossbar memory based on pull up resistors *Org. Electron.* 41 73–8

- [10] Stathopoulos S, Khiat A, Trapatseli M, Cortese S, Serb A, Valov I and Prodromakis T 2017 Multibit memory operation of metal-oxide bi-layer memristors *Sci. Rep.* 7 17532

- [11] Tan H W, Liu G, Yang H L, Yi X H, Pan L, Shang J, Long S B, Liu M, Wu Y H and Li R W 2017 Light-gated memristor with integrated logic and memory functions ACS Nano 11 11298–305

- [12] Tao Y, Wang Z Q, Xu H Y, Ding W T, Zhao X N, Lin Y and Liu Y C 2020 Moisture-powered memristor with interfacial oxygen migration for power-free reading of multiple memory states *Nano Energy* **71** 104628

- [13] Xu R J, Jang H, Lee M H, Amanov D, Cho Y, Kim H, Park S, Shin H J and Ham D 2019 Vertical MoS<sub>2</sub> double-layer memristor with electrochemical metallization as an atomic-scale synapse with switching thresholds approaching 100 Mv Nano Lett. 19 2411–7

- [14] Abunahla H, Jaoude M A, O'Kelly C J, Halawani Y, Al-Qutayri M, Al-Sarawi S F and Mohammad B 2018 Switching characteristics of microscale unipolar Pd/Hf/HfO2/Pd memristors *Microelectron. Eng.* 185–186 35–42

- [15] Chen M J, Dong G Y, Li X, Gao Z C, Feng H, Wang F H, Li G and Li X 2019 Influence of MoS<sub>2</sub> quantum dots size on the properties of memristor devices *Optik* 207 163776

- [16] Valov I and Lu W D 2016 Nanoscale electrochemistry using dielectric thin films as solid electrolytes *Nanoscale* 8 13828–37

- [17] Liu Y, Guo J, Zhu E B, Liao L, Lee S J, Ding M N, Shakir I, Gambin V, Huang Y and Duan X F 2018 Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions *Nature* 557 696–700

- [18] Yoon J H, Song S J, Yoo I H, Seok J Y, Yoon K J, Kwon D E, Park T H and Hwang C S 2014 Highly uniform, electroforming-free, and self-rectifying resistive memory in the Pt/Ta<sub>2</sub>O<sub>5</sub>//HfO<sub>2-x</sub>/TiN structure *Adv. Funct. Mater.* 24 5086–95

- [19] Cho D Y, Luebben M, Wiefels S, Lee K S and Valov I 2017 Interfacial metal–oxide interactions in resistive switching memories ACS Appl. Mater. Interfaces 9 19287–95

- [20] Lee J, Du C, Sun K, Kioupakis E and Lu W D 2016 Tuning ionic transport in memristive devices by graphene with engineered nanopores ACS Nano 10 3571–9

- [21] Wang M *et al* 2018 Robust memristors based on layered two-dimensional materials *Nat. Electron.* **1** 130–6

- [22] Liu Y, Huang Y and Duan X F 2019 Van der Waals integration before and beyond two-dimensional materials *Nature* 567 323–33

- [23] Loo Y L, Someya T, Baldwin K W, Bao Z N, Ho P, Dodabalapur A, Katz H E and Rogers J A 2002 Soft, conformable electrical contacts for organic semiconductors: high-resolution plastic circuits by lamination *Proc. Natl Acad. Sci. USA* 99 10252–6

- [24] Jung Y *et al* 2019 Transferred via contacts as a platform for ideal two-dimensional transistors *Nat. Electron.* 2 187–94

- [25] Zhao H et al 2017 Atomically thin femtojoule memristive device Adv. Mater. 29 1703232

- [26] Bhattacharjee S et al 2020 Insights into multilevel resistive switching in monolayer MoS<sub>2</sub> ACS Appl. Mater. Interfaces 12 6022–9

- [27] Yoon J H, Zhang J, Lin P, Upadhyay N, Yan P, Liu Y, Xia Q and Yang J J 2020 A low-current and analog memristor with ru as mobile species Adv. Mater. 32 1904599

- [28] Chang C F, Chen J Y, Huang C W, Chiu C H, Lin T Y, Yeh P H and Wu W W 2017 Direct observation of dual-filament switching behaviors in Ta<sub>2</sub>O<sub>5</sub>-based memristors *Small* 13 1603116

- [29] Masens C, Schulte J, Phillips M and Dligatch S 2000 Ultra flat gold surfaces for use in chemical force microscopy: scanning probe microscopy studies of the effect of preparation regime on surface morphology *Microsc. Microanal.* 6 113–20

- [30] Dash C S, Sahoo S and Prabaharan S R S 2018 Resistive switching and impedance characteristics of M/TiO<sub>2-x</sub>/TiO<sub>2</sub>/M nano-ionic memristor *Solid State Ion*. 324 218–25

- [31] Hua Q L, Wu H Q, Gao B, Zhang Q T, Wu W, Li Y J, Wang X H, Hu W G and Qian H 2019 Low-voltage oscillatory neurons for memristor-based neuromorphic systems *Glob. Challenges* 3 1900015

- [32] Lee S H, Park H L, Kim M H, Kang S J and Lee S D 2019 Interfacial triggering of conductive filament growth in organic flexible memristor for high reliability and uniformity ACS Appl. Mater. Interfaces 11 30108–15